## A Handbook on Design and Analysis of Novel Concurrent Cellular Automation Logic Block Observer BIST Structure

Er. Ravi Trivedi Dr. Sandeep Dhariwal Dr. Ravi Shankar Mishra Dr. Rajkumar Sarma

### A Handbook on Design and Analysis of Novel Concurrent Cellular Automation Logic Block Observer BIST Structure

First Edition

#### Authors

Er. Ravi Trivedi Dr. Sandeep Dhariwal Dr. Ravi Shankar Mishra Dr. Rajkumar Sarma

**INSC International Publishers**

Title of the Book: A Handbook on Design and Analysis of Novel Concurrent Cellular Automation Logic Block Observer BIST Structure

#### **Edition: First- 2021**

#### **Copyright 2021** © Authors

**Er. Ravi Trivedi,** Member of senior technical staff, Digicomm Semiconductors Pvt. Ltd., Pune

**Dr. Sandeep Dhariwal,** Associate Professor, ECE, Alliance College of Engineering and Design, Alliance University, Bengaluru, Karnataka.

**Dr. Ravi Shankar Mishra,** Professor & Head, Department of Electronics & Communication Engineering, Sagar Institute of Science & Technology (SISTec) Bhopal (M.P.) 462 036.

**Dr. Rajkumar Sarma,** Assistant Professor, EEE Department, FET, Jain (Deemed-to-be-University), Bangalore.

No part of this book may be reproduced or transmitted in any form by any means, electronic or mechanical, including photocopy, recording or any information storage and retrieval system, without permission in writing from the copyright owners'.

#### Disclaimer

The authors are solely responsible for the contents published in this book. The publishers or editors don't take any responsibility for the same in any manner. Errors, if any, are purely unintentional and readers are requested to communicate such errors to the editors or publishers to avoid discrepancies in future.

#### E-ISBN: 978-1-68576-081-6

#### MRP Rs. 200/-

**PUBLISHER & PRINTER: INSC International Publishers**

Pushpagiri Complex, Beside SBI Housing Board, K.M. Road Chikkamagaluru, Karnataka Tel.: +91-8861518868 E-mail: info@iiponline.org

#### **IMPRINT: IIP**

# Dedicated to

#### Preface

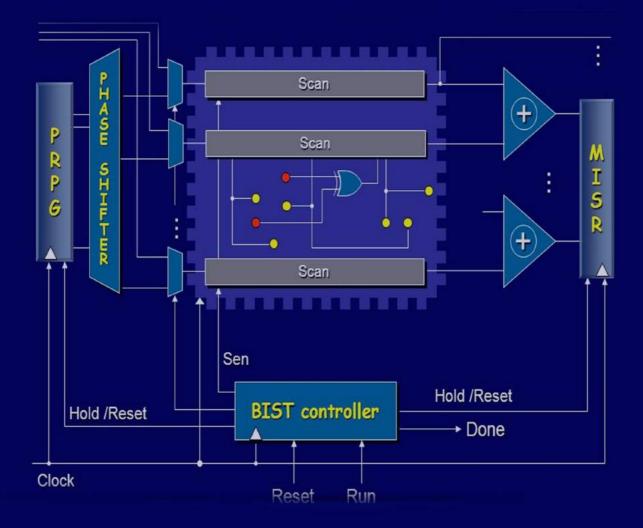

An efficient Design for Testability (DFT) has been a major concern for today's VLSI engineers. A poorly designed DFT would result in losses for manufacturers with a considerable rework for the designers. Built-in Self-Test (BIST) - One of the promising DFT techniques is rapidly modifying with the advances in technology as device shrinks. Because of the growing complexities of the hardware, the trend has shifted to include BISTs in high performance circuitry for offline as well as online testing. Work done here involves testing various Circuit Under Test (CUT) with different techniques of built in response analyzer and vector generator with a monitor to control all the activities. Use of low transition vector generators like Bit-Swapping Complete Feedback Shift Register (BS-CFSR), Cellular Automata Registers (CAR), Concurrent Built-In Logic Block Observer (CBILBO), and, novel design Concurrent Cellular Automata Logic Block Observer (CCALBO) an effort is made to reduce power consumption by comparing it to classical Linear Feedback Shift Register (LFSR) techniques. This book presents the process of design implementation for a complete BIST working on both normal operation mode as well as test mode for multiple circuitry like Carry Look Ahead (CLA) adder, ISCAS benchmark circuits (74XX series) - 74181 and 74283, Vedic Multiplier, and Multiply and Accumulate processor. A thorough comparison is carried out by comparing all the DFT techniques with each other. Xilinx Vivado 2018.1 for coding in Verilog and implementation with Cadence's Encounter(R) RTL Compiler RC 14.10 were used for timing responses, area calculations, and power consumption at different technology nodes.

> Er. Ravi Trivedi Dr. Sandeep Dhariwal Dr. Ravi Shankar Mishra Dr. Rajkumar Sarma

#### Acknowledgement

With deep regards and profound respect, we avail this opportunity to express our deep sense of gratitude to thank all our friends for timely completion of the book.

Last but not least, we also convey our deepest gratitude to our parents for whose faith, patience and teaching had always inspired us to walk upright in our life.

Finally, we humbly bow our head with utmost gratitude before the God Almighty who always showed us a path to go and without whom we could not have done any of these.

> Er. Ravi Trivedi Dr. Sandeep Dhariwal Dr. Ravi Shankar Mishra Dr. Rajkumar Sarma

#### Contents

| Chapter 1 | Introduction to BIST                                 | 1-5   |

|-----------|------------------------------------------------------|-------|

| 1.1       | Basics of Testing                                    | 1     |

| 1.1.1     | The Testing Problem                                  | 2     |

| 1.2       | BIST and its operation                               | 3     |

| 1.2.1     | Basic BIST Architecture                              | 4     |

| 1.2.2     | Advantages and Disadvantages of BIST                 | 5     |

| 1.3       | Scope of the work                                    | 5     |

| Chapter 2 | Literature Review                                    | 6-8   |

| Chapter 3 | Automatic Test Pattern Generation                    | 9-17  |

| 3.1       | Linear Feedback Shift Register                       | 9     |

| 3.2       | Bit Swapping Complete Feedback Shift Register        | 12    |

| 3.3       | Cellular Automata                                    | 14    |

| 3.4       | Comparing ATPGs                                      | 16    |

| Chapter 4 | <b>Output Compaction and Signatures</b>              | 18-21 |

| 4.1       | Comparators                                          | 19    |

| 4.2       | Counter-based ORAs                                   | 19    |

| 4.3       | Signatures                                           | 20    |

| 4.3.1     | Multiple Input Signature Register                    | 21    |

| Chapter 5 | <b>Built-in Logic Block Observer</b>                 | 22-25 |

| 5.1       | Built-In Logic Block Observer                        | 22    |

| 5.1.1     | Concurrent Built-in Logic Block Observer             | 23    |

| 5.1.2     | Cellular Automata Logic Block Observer               | 24    |

| 5.1.3     | Concurrent Cellular Automata Logic Block<br>Observer | 25    |

| Chapter 6 | Circuit Under Test                                   | 26-31 |

| 6.1       | 74XX Circuits                                        | 26    |

| 6.2       | Vedic Multiplier                                     | 28    |

| 6.3       | Multiply and Accumulate processor                    | 30    |

| Chapter 7 | <b>RTL Analysis</b>      | 32-45 |

|-----------|--------------------------|-------|

| Chapter 8 | Analysis and Discussions | 46-59 |

| 8.1       | Timing Responses         | 46    |

| 8.2       | Power and Area Analysis  | 50    |

| 8.3       | Delay Analysis           | 57    |

| 8.4       | Fault Coverage Analysis  | 58    |

| 8.5       | Future Scope             | 58    |

|           | References               | 60-61 |

|           | Acronyms                 | 62    |

#### **About the Authors**

**Mr. Ravi Trivedi** received his M.Tech degree from Lovely Professional University (Punjab). He has published several research papers in reputed conferences and journals. At present, he is working as senior technical staff member in Digicomm Semiconductors Pvt. Ltd., Pune in the field of Broadcom Inc. client. His area of research includes Physical Verification, VLSI Testing, STA.

**Dr. Sandeep Dhariwal** received his B.E. in 2004 from C.R.S.C.E. Murthal (M.D.U. Rohtak) in ECE. He completed his M.Tech from G.J.U.S.T. Hisar in 2008 in VLSI Design and Embedded Systems. He completed his Ph.D. in 2015 from Banasthali University- Banasthali (Rajasthan) in Electronics Engineering. Currently he is working as an associate professor in ACED, Alliance University (central Campus) Bengaluru (INDIA). His area of research includes low power VLSI design, Testing of VLSI circuits,

Digital VLSI Design. He has published many research articles in reputed national and international journals and conferences.

**Dr. Ravi Shankar Mishra** has received his Ph.D. in 2011 and M.Tech. in 2005 from N.I.T. Bhopal. He has completed his PG Diploma in VLSI Design from C-DAC Bangalore. He has 19+ years of research and academic experience in repute institutions such as Lovely Professional University (LPU) Punjab, Symbiosis University of Applied Sciences (SUAS), Indore, Guru Nanak Institute of Technology (GNIT) Hyderabad. He has handled the important position of responsibilities like Dean, Head of Department,

Research Coordinator, etc. He has published more than 40 research papers in reputed international journals and international conference proceedings including SCI, Scopus. He is also a reviewer of many Journals. One copyright and two books are registered with his name. He has supervised 3 Ph.D. scholars and 18 dissertations at the PG level. He is a Life Fellow Member of the Institution of Electronics & Telecommunication Engineers (IETE) and International Association of Engineers (IAENG). His research contributions have been in the area of designing efficient PUF based circuits to using CMOS for generating the secure key.

**Dr. Rajkumar Sarma** received his B.E. in Electronics and Communications Engineering from Vinayaka Mission's University, Salem, India in 2008. He received his M.Tech as well as Ph.D. degrees from Lovely Professional University, Phagwara, Punjab in the years 2012 & 2020 respectively. He is working as an Assistant Professor (Senior Grade) in the School of Electrical and Electronics Engineering, Jain (Deemed - To- Be - University), Ramanagara, Karnataka. His research

interests include Analog and Digital VLSI design, Prototype development using FPGA etc. The author has around 20+ research publications in SCI/Scopus indexed reputed Journals and national/international Conferences. Moreover, the author has 15+ patents/copyrights published in various engineering fields. He has also authored and edited several books and book chapters from reputed publishers.

e-ISBN:978-1-68576-081-6

MRP Rs.200/-

Selfypage Developers Pvt Ltd.